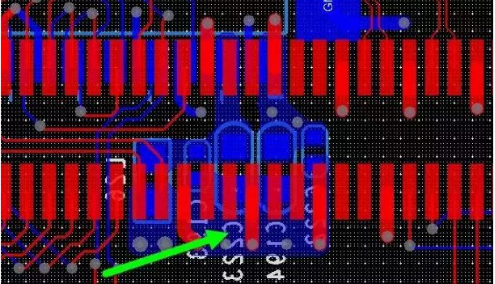

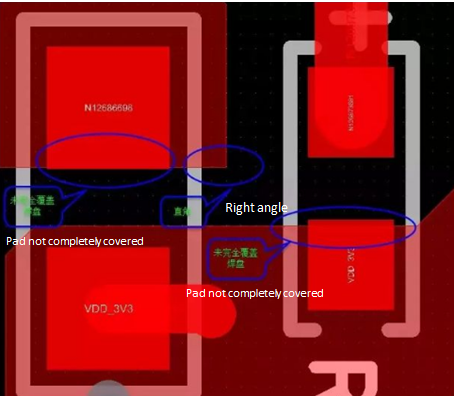

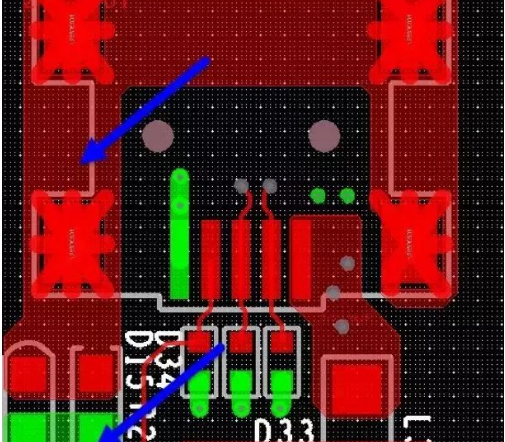

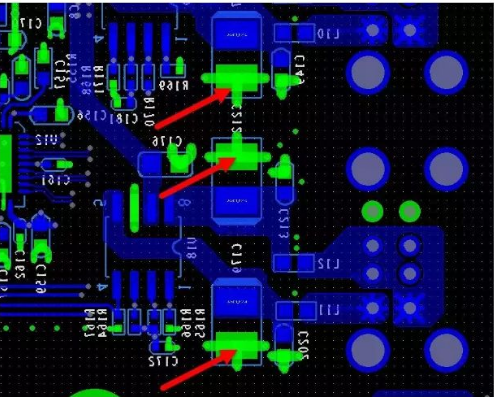

1. When the copper covers the pad, it must be completely covered, and the shape and the pad cannot form an acute angle.

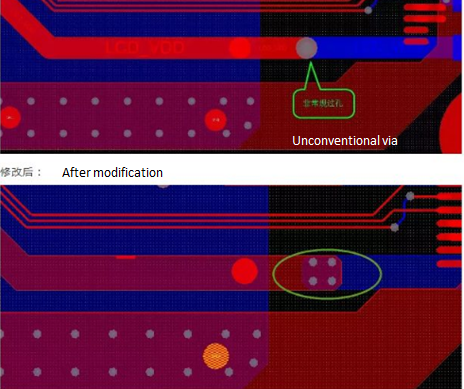

2.Try to replace the thick line with copper. When thick lines are used, the vias are typically preferably non-normal trace vias, increasing the aperture and pads of the vias.

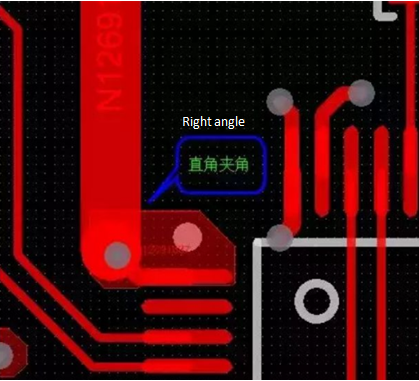

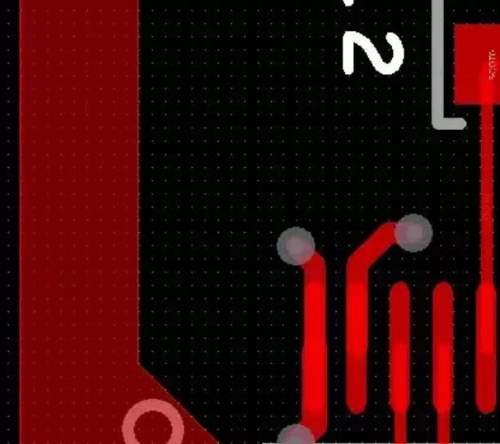

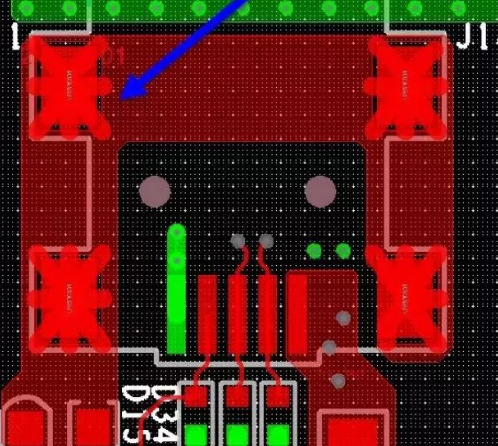

3. Try to replace the copper + trace pattern with copper. The latter often produces small sharp corners and right angles to replace the traces with copper:

After modification:

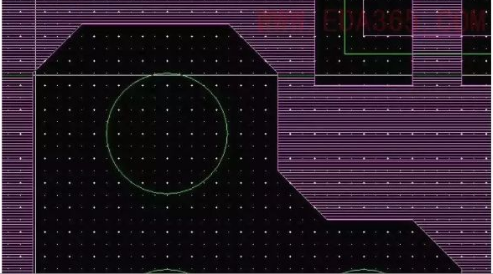

4.The boundary of the shape must be on the grid point, and grid-off is not allowed. (sony specification)

5.The shape corner must be the same size. As shown in the figure below, the corners of the corner are 4 grid points, so all the small corners must do this. (sony specification)

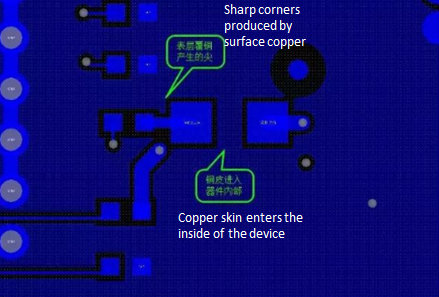

1.The shape cannot cross the pad and enter the inside of the device, in particular, the surface is covered with a large range of copper. (sony specification)

2.Strictly speaking, shape&shape, shape&line must be equally spaced. If you set shape and line0.3mm, spacing, then all the shape spacing should be the same, there can be no such thing as 0.4mm or 0.25mm, but in order to keep the grid Copper is the grid spacing under the premise of satisfying the 0.3mm pitch. (sony specification)

3.The outer casing of the plug, and the inductance connected to the outer casing and the GND at the other end of the resistor are preferably copper-clad.

4.The copper connection of the outer casing of the plug is preferably in the form of an 8-angle, not a Full Connect.

5.The GND end of the capacitor preferably enters the inner layer directly through the via hole, not through the copper skin connection, the latter is not conducive to soldering, and the copper skin in a small area is meaningless.

6. The connection of the power supply, especially the power supply pin output from the power chip, is preferably connected by copper.

7.PCB, even if there are a lot of blank areas, if the spacing of the signal lines is large enough, there is no need to cover the copper floor. Partial copper coating on the surface layer will cause uneven copper balance on the board. And if the copper is too close to the trace, the impedance of the trace will be affected by the copper.

8.Due to the tight space, GND can't enter the inner layer through the via hole. At this time, it can be partially covered with copper and then connected through the via and the inner layer.